|

||||||||||||||||

| <Добавить в Избранное> <Сделать стартовой> <Реклама на сайте> <Контакты> | ||||||||||||||||

|

||||||||||||||||

| ||||||||||||||||

|

| ||||||||||||||||

Компьютеры -> Процессоры -> Fall Processor Forum 2005: процессоры завтрашнего дня | ||||||||||||||||

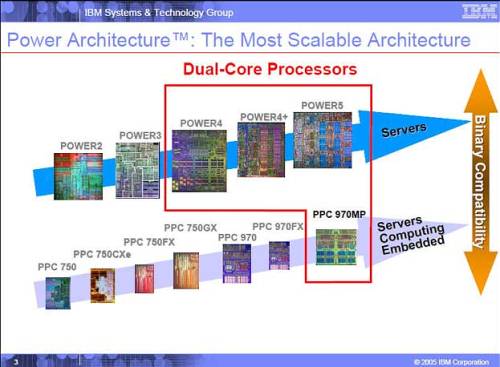

Fall Processor Forum 2005: процессоры завтрашнего дняОдно из самых интересных, на мой взгляд, технологических событий 2005 года – прошедший в последнюю неделю октября Fall Processor Forum 2005, (FPF, ранее - Microprocessor Forum). Форум посвящен, как видно из названия, новым архитектурам процессоров и проводится традиционно два раза в год аналитической компанией In-Stat/MDR при активном участии, содействии и спонсорстве большинства производителей полупроводниковой промышленности, так или иначе связанных с процессорами. Влияние мероприятий класса Processor Forum на индустрию весьма велико, многие компании стараются приурочить анонс новых процессорных архитектур именно к этому событию. Отмечу, что именно в рамках майских сессий конференции Spring Processor Forum 2005 впервые были представлены детали архитектуры чипов IBM Cell и Broadband Engine Processor, а годом ранее, в дни проведения конференции Fall Processor Forum 2004, мы впервые узнали подробности о 2-ядерных процессорах AMD, 64-битной архитектуре чипа VIA Isaiah, втором и третьем (ныне мёртвом) поколении чипов Efficeon от компании Transmeta. На сессии Fall Processor Forum 2005 от производителей x86 процессоров для настольных, мобильных и серверных систем последовал лишь один единственный доклад – Pacifica: x86 Architectural Enhancements to Facilitate Virtualization, зачитанный Кевином МакГратом (Kevin McGrath) из AMD. Судя по пресс-релизам октября, AMD сейчас больше занята вопросами продвижения архитектур Geode и Alchemy, а также промо-акциями в пользу новой 15-месячной программы AMD Commercial Channel Program. В нашем сегодняшнем рассказе не будет подробностей о внедрении технологии виртуализации AMD Pacifica, полагаю, мы коснемся этой темы несколько позже в соответствующем комплексном материале по архитектуре процессоров Opteron. Остальные производители x86 архитектур на FPF 2005 не выступали, как говорится, "одних уж нет, а те далече". Компания Intel традиционно проводит анонсы своих новых архитектур в рамках собственного технологического форума для разработчиков – IDF. Компании VIA, хранившей последний год гробовое молчание о подвижках в разработке ядра VIA Isaiah и только собирающейся начать массовые поставки процессоров VIA C7/C7M, скорее всего, особенно рассказывать не о чем. Уж молчу об архитектуре Transmeta Efficeon, следы которой потерялись весной 2005 года в Гонконге, после продажи интеллектуальных прав на Crusoe/Efficeon гонконгской компании Culture.com Technology, дочернему предприятию инвестиционной компании Culturecom Holdings, вкладывающей деньги во всё - от китайских комиксов до процессоров. Впрочем, тот факт, что архитектура x86 фактически "выпала" из интересов Fall Processor Forum 2005, совершенно не умаляет значимости сессий форума, ибо современные тенденции энергичного роста спроса на современную бытовую компьютерную технику и портативную электронику подразумевают параллельное развитие множества самых разнообразных архитектур CPU. Начиная с прошлого года были объединены сразу три конференции, считавшиеся ранее самостоятельными - Microprocessor Forum, Embedded Processor Forum и MEMS Executive Forum. Таким образом, в течение одной рабочей недели участники Fall Processor Forum 2005 получают возможность узнать сразу всё о новых и зачастую достаточно взаимосвязанных технологиях в области разработки микропроцессоров, встраиваемых процессоров и Микро-Электро-Механики (MEMS). Список сессий, состоявшихся в рамках Fall Processor Forum 2005 и проходивших под общим лозунгом The Road To Multicore, впечатляет: были представлены новые поколения серверных чипов, процессоров для встраиваемых систем, DSP и многое другое. Для справки лишь перечислю список компаний, отметившихся в рамках FPF 2005 с докладами. Это Broadcom, Fujitsu Limited, P. A. Semi, Hardware Engineering, Azul Systems, ARM, Innovative Silicon, ARC International, Tensilica, videantis GmbH, Microsoft, Green Hills Software, XenSource, AMD, Freescale, S-T-I Design Center, IBM, Texas Instruments, Fulcrum Microsystems, Sonics. В этом кратком дайджесте событий FPF 2005 ограничусь рассказом лишь о самых интересных докладах конференции, ибо остальные материалы, на мой взгляд, интересны лишь узким специалистам. Архитектура IBM PowerPC для Microsoft Xbox 360В дни Fall Processor Forum 2005 компания IBM - генеральный спонсор мероприятия, представила четыре доклада из 19 прозвучавших. Ключевыми стали рассказы о разработке специализированного CPU для Microsoft Xbox 360, экономичного 2-ядерного процессора IBM PowerPC 970MP; наряду с этим был представлен детальный анализ дизайна процессора Cell.

Ключевым событием, конечно же, стал анонс IBM нового процессора, специально разработанного для использования в составе игровой консоли Microsoft Xbox 360. Производство нового процессора уже начато, при этом сразу на двух предприятиях - собственной фабрике IBM в Ист-Фишкилл (East Fishkill), Нью-Йорк, и фабрике контрактного производителя чипов Chartered Semiconductor Manufacturing в Сингапуре. Процессор был разработан менее чем за 24 месяца после заключения осенью 2003 года контракта с Microsoft. Процессор Xbox 360, разработанный совместной командой специалистов из IBM и Microsoft, представляет собой чип SoC (System-on-Chip), выполненный на базе специализированного варианта известного 64-битного ядра IBM PowerPC, схожего по архитектуре с Cell (см. нашу статью Процессор Cell: шаг в будущее) или PowerPC970, но с некоторыми важными особенностями. Точнее, в случае Xbox 360 в чип интегрированы три идентичных ядра PowerPC с тактовой частотой 3,2 ГГц, объединенные диспетчерской шиной XBAR, с возможностью обработки двух независимых тредов каждым. Таким образом, в случае Xbox 360 можно говорить о возможности одновременной обработки до шести потоков данных. Разработчики IBM позаботились о возможности снижения тактовой частоты в случае неполной загрузки чипа, что снижает энергопотребление в режиме ожидания.

Архитектура чипа Xbox 360 Процессор Xbox 360 состоит из 165 млн. транзисторов, площадь ядра составляет 168 мм². Для снижения энергопотребления и увеличения производительности используется 90 нм технологический процесс IBM CMOS 10 KE с применением технологии SOI (Silicon on Insulator).

Архитектура системной шины (FSB) Особенность архитектуры процессора Xbox 360, предусмотренная для увеличения производительности игровой консоли Microsoft Xbox 360 и борьбы с неизбежными задержками – системная шина (Front Side Bus, FSB) с пропускной способностью до 21,6 Гб/с. Системная шина разделена на два виртуальных канала, каждый состоит из двух линий (lanes), оба канала являются двунаправленными. Соответственно, производительность каждой линии составляет 5,4 Гб/с, в сумме - до 21,6 Гб/с, соответственно, по 10,8 Гб/с на каждый канал. Впрочем, поскольку процессор и графический чип работают на разных тактовых частотах, общение через FSB носит асинхронный характер. Потери и задержки удалось свести к минимуму ещё и за счет того, что память к чипу IBM Xbox 360 напрямую не подключена.

Взаимодействие блоков чипа Xbox 360 Чип обладает 32 Кб 2-направленного 128-битного кэша инструкций L1 на каждое ядро и 32 Кб такого же кэша данных L1 на каждое ядро. Ключевое требование к процессору, специально "заточенному" под игровые и мультимедийные приложения - возможность обработки мощных объемов потоковых данных.

Оптимизация обработки потоковых данных xDCBT - eXtended Data Cache Block Touch Вот почему в чипе Xbox 360 реализована возможность обхода кэша L2, с пересылкой до восьми пакетов данных предварительной выборки (prefetch) непосредственно в кэш L1 каждого из трёх ядер процессора, при этом части кэша L2 могут быть распределены в качестве буферов для потоковых данных.

Возможности использования распределенного кэша L2 Графическое ядро может считывать данные непосредственно из кэша L2 процессора пакетами по 128 байтов. Кэш L2 размером 1 Мб на базе специальной логики для поддержки скоростных потоков графических данных и системных приложений распределен между тремя ядрами процессора, работа с данными осуществляется на полной тактовой частоте процессора, то есть, 3,2 ГГц, в то время как управляющая логика и буферы (Transaction Layer) работают на половинной тактовой частоте - 1,6 ГГц.

Комбинированный модуль VMX и FPU Каждое из трёх ядер процессора имеет скоростной 128-битный векторный модуль VMX (Vector/SIMD Multimedia eXtention). В чипе Xbox 360 количество векторных регистров VMX увеличено с 32 (у стандартных ядер PowerPC) до 128. Модуль VMX обрабатывает одновременно два потока, при этом в чипе Xbox 360 реализована поддержка дополнительного набора инструкций для ускорения обработки 3D игровых приложений и потоковых данных, вроде инструкций Direct3D-Pack и Unpack. Имеется стандартный FPU, объединенный с модулем VMX, но похоже, что большинство инструкций с плавающей запятой обрабатываются все же с помощью модуля VMX.

Межпроцессорная шина DataLink Layer является 64-битной и работает на тактовой частоте 1,35 ГГц. В целом дизайн приставки Xbox 360 разрабатывался с прицелом на то, чтобы процессор и графический чип были равноправными партнерами системы, в отличие от классического Wintel PC, где традиционно в центре системы исключительно процессор. Вот почему системная память и южный мост подключены к графическому чипу от ATI, а не к процессору, вот почему процессор общается с графическим чипом ATI непосредственно по системной шине, а шина графического ядра Link Layer работает на тактовой частоте 675 МГц. Тактовая частота Transaction Layer графического процессора, схожа с тактовой частотой интерфейса 128-битной памяти GDDR3.

Корпусировка Xbox 360 Остается добавить, чипы Xbox 360 выпускаются в корпусе FC-PBGA габаритами 31 х 31 мм. Массовые поставки игровой консоли Microsoft Xbox 360 в США, Японии и Европе приурочены к сезону рождественских продаж 2005 года. В частности, в Германии начало продаж Microsoft Xbox 360 ожидается 2 декабря. В Европе Microsoft Xbox 360 будет продаваться по цене 299 евро в стандартной версии - с джойстиком и обычным AV кабелем.

Microsoft Xbox 360 Расширенный вариант Microsoft Xbox 360 по цене 399 евро будет иметь несколько измененный внешний дизайн, встроенный 20 Гб винчестер, контроллер беспроводной сети, в комплекте будут поставляться наушники, специальный HD-AV кабель с поддержкой High Definition видео. Ограничсенным тиражом также будет поставляться вариант Xbox-Live-Silver с Windows Media Center Edition 2005. Двухядерный процессор IBM PowerPC 970MPПредставленный в рамках Fall Processor Forum 2-ядерный процессор PowerPC 970MP не является чем-то экстраординарно новым: нынче этот чип в 2,5 ГГц версии поставляется в составе компьютеров Power Mac G5 Quad от Apple Computer. Однако, IBM PowerPC 970MP отличается использованием ряда новейших технологий, в частности, направленных на снижение энергопотребления, о чем обязательно стоит рассказать.

Архитектура IBM PowerPC 970MP Инициатива Intel, получившая название "Performance per Watt", в реализации PowerPC 970MP достигается несколькими способами. Один из простых и наиболее эффективных способов снижения энергопотребления практически вполовину – выключение одного из ядер в режиме простоя. Более того, за счет классического динамичного снижения тактовой частоты вполовину или на четверть также удаётся значительным образом снизить расход энергии – с пиковых 100 Вт до 60 Вт или даже до 40 Вт. Ещё одно интересное инженерное решение – переход процессора из полномасштабного в низковольтный режим, то есть, реализация в одном чипе обычного и low-voltage режима, с различными режимами "сна" - Nap и Deep Nap.

Переключение режимов IBM PowerPC 970MP Результаты впечатляют: в так называемом режиме "deep nap" (буквально "глубокого сна") процессор снижает тактовую частоту до 1/4 от номинала, при этом оба ядра активны - лишь "заторможены" до состояния "спячки", и общее энергопотребление чипа снижается до 5 Вт, при работе только одного ядра – до 3 Вт.

Типовое энергопотребление PowerPC 970MP Каждое ядро процессора PowerPC 970MP обладает своим собственным 1 Мб кэшем L2 (512 Кб у PowerPC 970FX), объединенным общей шиной. Это как раз и позволяет при возможности совершенно безболезненно отключать или уводить "в спячку" одно из ядер чипа. Тактовые частоты ядер регулируются синхронно, зато каждое ядро в отдельности обладает независимыми термодиодами и шинами питания. Процессоры PowerPC 970MP будут поставляться на рынок в версиях с тактовой частотой от 1,2 ГГц до 2,5 ГГц и выше. Оценочная производительность 2,5 ГГц чипа PowerPC 970MP составляет 9250DMIPS на ядро, при этом энергопотребление не превышает 100 Вт, пиковое энергопотребление 1,2 ГГц версии процессора составит всего 25 Вт. Чипы PowerPC 970MP будут поставляться в 575-контактных корпусах CBGA с уменьшенным содержанием свинца, габариты чипов составят 25 х 25 мм. Производство чипов налажено на фабрике IBM с применением 10-уровневого 90 нм CMOS техпроцесса, с использованием меди, напряженного кремния, low-k диэлектриков и технологии SOI.

Таким образом, можно сказать, что двуядерный процессор PowerPC 970MP представляет собой в какой-то степени "римейк" IBM по мотивам Power4, со значительно улучшенными режимами управления энергопотреблением. Ибо несмотря на то, что предшественниками PowerPC 970MP являются одноядерные PowerPC 970 и 970FX, общим "предком" этой серии был процессор IBM Power4 – самый первый серверный многоядерный чип, представленный ещё в 2001 году. Ожидается, что процессоры PowerPC 970MP будут представлены в первом квартале 2006 года в составе blade-серверов IBM.

P.A.Semi PWRficient PA6T-1682M: экономичный 2-ядерный процессор на базе архитектуры PowerPCЕщё один способ использования архитектуры Power, применяемой нынче в серверах IBM и компьютерах Apple Mac, предложила в рамках прошедшего форума начинающая калифорнийская компания P.A. Semi. Первая разработка компании - чип PWRficient, обладает двумя ядрами, работает на тактовой частоте 2 ГГц и при этом в типичном режиме нагрузки потребляет всего 7 Вт, а в пике – не более 25 Вт. Запомните этот логотип, не исключено, что в последующие годы он будет достаточно часто мелькать в новостях.

Архитектура PWRficient По словам Дэна Добберпула (Dan Dobberpuhl), CEO компании P.A. Semi, режимы энергосбережения, реализованные в архитектуре PWRficient, значительно более эффективны нежели в системах на базе чипов Intel Xeon или AMD Opteron. Так, 4000-процессорный кластер на базе серверов с PWRficient за три года "съест" электричества примерно на $360 тысяч, в то время как эквивалентные системы на чипах Xeon и Opteron "потратят" до $3 млн. и $3,5 млн. соответственно.

Экономия энергии - краеугольный камень PWRficient Архитектура PWRficient выглядит многообещающе. Тем более, что в составе P.A. Semi собралась достаточно бывалая команда: Дэн Добберпул, работая в незапамятные времена в DEC (Digital Equipment Corp.), принимал непосредственное участие в разработке процессорных архитектур Alpha и StrongARM, Джим Келлер (Jim Keller) и Пит Бэннон (Pete Bannon), вице-президенты P.A. Semi, также принимали непосредственное участие в разработке архитектуры Alpha, а Келлер к тому же успел потрудиться в AMD над созданием архитектуры Opteron. Кстати, первоначально P.A. Semi именовалась как Palo Alto Semiconductor, но после переезда компании из Пало-Альто в Санта-Клару имя пришлось несколько подкорректировать.

PA6T-1682M Дизайн PWRficient - не обычная переработка лицензированной у IBM архитектуры PowerPC, как это частенько бывает, например, с ядрами, лицензированными у MIPS. В отличие от множества конкурентов, разрабатывающих чипы для приложений преимущественно коммуникационного сектора и устройств аппаратной защиты, инженеры P.A. Semi разработали PWRficient для применения в широком списке устройств, включая телевизионные приставки, игровые консоли, принтеры, системы хранения данных, серверы, автомобильную электронику и т.п.

PA6T-1682M Основой архитектуры чипов PWRficient является процессорное ядро PA6T, внутренняя шина Conexium и подсистема I/O под названием ENVOI. Суперскалярное Out-of-Order ядро PA6T с 19-стадийным конвейером способно выполнять до трех инструкций одновременно. CONEXIUM по сути своей представляет оригинальную системную шину, связывающую процессорное ядро, кэш L2, контроллеры памяти и I/O модуль ENVOI. Достаточно интересно в этой архитектуре реализован кэш. В отличие от большинства многоядерных процессоров, где ядра обладают раздельным кэшем или единым распределенным кэшем, архитектура P.A. Semi подразумевает передачу данных с использованием шины Conexium – этакого "внутрипроцессорного интернета".

Процессоры PWRficient являются решениями с высокой степенью интеграции, включая в себя как своеобразный северный мост с контроллером памяти, так и южный мост, позволяющий подключать разнообразную периферию. Так, представленный на конференции чип PWRficient 1682M обладает 2 Мб кэша L2, интегрированным контроллером памяти DDR2, блок ENVOI поддерживает 8 линий PCI Express, два порта 10Gbit Ethernet и множество других интерфейсов. Неплохо, однако в последствии проблемой столь мощно интегрированного дизайна может стать недостаточная поддержка всего комплекса востребованных периферийных стандартов. Наряду с 2-ядерным процессором 1682M, в компании P.A. Semi также разрабатывают всевозможные вариации на базе своей архитектуры, от одноядерных до 8-ядерных чипов. Согласно стратегии P.A. Semi, чипы будут выпускаться в трех различных вариантах корпуса – для high-end (4–8 ядер), среднего (1–4 ядра) и low-end (1–2 ядра) рынков.

"Дорожная карта" P.A. Semi Несмотря на то, что образцы первого чипа с архитектурой PWRficient - PA6T-1682M, появятся не раньше третьего квартала 2006 года, а массовые поставки начнутся не ранее чем через два года, в P.A. Semi уже сейчас планирует сразу же перескочить на использование 65 нм техпроцесса. При этом, в отличие от большинства конкурентов, размещающих заказы у азиатских производителей, P.A. Semi намерена сотрудничать с североамериканской компанией, пока неназванной. Freescale e600: 2-ядерный PowerPC для встраиваемых системЕщё один чип на базе архитектуры IBM PowerPC, представленный в дни Fall Processor Forum 2005 компанией Freescale Semiconductor (бывшее подразделение Motorola, отделившееся в самостоятельное предприятие по выпуску полупроводников) - 2-ядерный MPC8641D из семейства Freescale e600.

Архитектура Freescale MPC8641D В семейство процессоров Freescale e600 с архитектурой PowerPC уже входят два одноядерных чипа - MPC7448 и MPC8641. Новый чип MPC8641D сочетает в себе два ядра e600, два 1 Мб кэша L2, двойной векторный модуль AltiVec, а также интегрированную шину MPX. Наряду с этим чип MPC8641D обладает двумя интегрированными контроллерами памяти с поддержкой стандартов DDR и DDRII, а также рядом встроенных скоростных интерфейсов - RapidIO, PCI Express, Gigabit Ethernet и т. п. Процессорные ядра MPC8641D работают на частотах от 1,0 ГГц до 1,7 ГГц, 64-битная интегрированная шина MPX - на частоте до 667 МГц. Имеется 32 Кб кэша инструкций L1 и 32 Кб кэша данных L1 (на ядро), 1 Мб кэша L2 на ядро с опциональной поддержкой ECC. Чипы производятся с соблюдением 90 нм техпроцесса с SOI и выпускаются в термостойком керамическом корпусе HiTCE. Заявленное энергопотребление 2-ядерной 1,7 ГГц версии чипа MPC8641D – не более 60 Вт, low-voltage версии с тактовой частотой 1,4 ГГц – порядка 22 Вт. Предполагается, что двуядерные чипы Freescale MPC8641D будут использоваться в системах хранения данных, сетевых, телекоммуникационных, военных и прочих приложениях. Olympus и Jupiter – многоядерные чипы Sparc64 от FujitsuТеперь поговорим о грандиозных планах Fujitsu, завтрашних, послезавтрашних и совсем отдаленных.

Планы выпуска процессоров семейства Fujitsu Sparc64 Напомню, что после заключенного в 2004 году соглашения, Sun Microsystems отказалась от работ над UltraSparc V в пользу чипов Niagara и совместного серверного high-end проекта Advanced Processor Line (APL), где будут использоваться процессоры Sparc64 производства Fujitsu. В настоящее время компания Fujitsu использует свои чипы Sparc64 в UNIX серверах серии PRIMEPOWER. В августе одноядерный чип Sparc64 V был отмечен японским премьер-министром в качестве передовой японской разработки. Сейчас одноядерные процессоры Sparc64 V+ производятся с применением норм 90 нм техпроцесса, а тактовые частоты чипов уже достигли 2,16 ГГц.

Двуядерный Sparc64 VI Olympus Согласно представленному на конференции плану развития семейства Sparc64, во второй половине 2006 года программа APL получит первые 2-ядерные чипы под кодовым названием Olympus, выполненные на базе процессорной архитектуры Fujitsu Sparc64 VI. В настоящее время стадия разработки чипа Olympus завершена, документация уже передана производственникам. Ради справедливости стоит отметить, что и здесь не обошлось без задержек, так как на Fall Processor Forum 2003 представители Fujitsu обещали выпустить Olympus во второй половине 2005 года. Двуядерный чип Sparc64 VI Olympus будет производиться с соблюдением норм 90 нм техпроцесса, будет обладать общим распределенным кэшем L2 размером 6 Мб и тактовыми частотами порядка 2,4 ГГц, при этом площадь кристалла составит 423 мм², а энергопотребление – примерно 120 Вт.

4-ядерный Sparc64 VI+ Jupiter К 2008 году компания Fujitsu пообещала представить 4-ядерный процессор Sparc64 VI+ с рабочим названием Jupiter, с тактовой частотой минимум 2,7 ГГц, отдельным кэшем L1 для каждого ядра и распределенным кэшем L2 для всех четырех ядер. Об этом чипе пока известно достаточно мало. Например, уже известно, что для коммуникаций между процессором Jupiter и чипсетом будет использоваться новая системная шина, но пока неизвестно, какого типа и с какой производительностью. Как было объявлено в докладе на Fall Processor Forum, Fujitsu планирует производить процессоры Jupiter с соблюдением норм 65 нм техпроцесса с 10-слойной металлизацией и применением меди, при этом площадь ядра все равно окажется просто громадной – порядка 460 мм², поскольку чип будет состоять из 540 млн. транзисторов. Чип будет выпускаться в 412-контактном корпусе, ожидаемое пиковое энергопотребление Sparc64 VI+ Jupiter – порядка 120 Вт. Плюсом процессорных архитектур Sparc64 VI и Sparc64 VI+ является использование схожих шин обмена данными, что позволяет надеяться на обратную совместимость новых чипов с ранее выпущенными системами. Представители Fujitsu напрямую не подтвердили гарантию такой совместимости, но отметили, что по крайней мере, имеют подобные планы.

Vertical Multithreading Изюминка многоядерных чипов Sparc64 – поддержка технологии многопоточной обработки данных, получившая в Fujitsu название VMT, или Vertical Multithreading. Двуядерные чипы архитектур Sparc64 VI и Sparc64 VI+ смогут одновременно исполнять до двух последовательностей инструкций (тредов) для каждого ядра, переключаясь на обработку второго треда в случае отсутствия данных на обработку первого в кэше (cache miss).

Vertical Multithreading По данным представителей Fujitsu, применение технологии VMT дает как минимум 20% прирост производительности. В перспективе все процессоры семейства Sparc64 будут многоядерными и будут поддерживать многопоточную обработку данных. По крайней мере, чипы серии Sparc64 VI Olympus будут обрабатывать до четырех тредов, чипы серии Sparc64 VI+ Jupiter - до восьми тредов. Cortex-A8 - Tiger: первое явление архитектуры ARMv7В дни Fall Processor Forum 2005 английская компания ARM выступила с подробным докладом об архитектуре представленного в начале октября на второй ARM Developers Conference процессора Cortex-A8, фигурировавшего в стадии разработки под рабочим названием Tiger. Новый экономичный процессор ARM Cortex-A8 предназначен для использования в составе мобильных и бытовых устройств, работающих с многоканальными видео, аудио и игровыми приложениями, например, телефонов нового поколения.

Архитектура Cortex-A8 Чип Cortex-A8 представляет собой первую разработку на базе новой архитектуры ARMv7. Производительность и экономичность обеспечиваются поддержкой технологии Thumb-2, а также впервые интегрированными процессорными расширениями серии NEON (FPU/DSP, 64-бит SIMD) для улучшения работы с кодеками класса H.264 и MP3. Наряду с этим, чипы Cortex-A8 также включают в себя поддержку технологии Jazelle-RCT Java для оптимизации и ускорения обработки Just In Time (JIT) и Dynamic Adaptive Compilation (DAC), снижая нагрузку на память в три раза. Новый процессор также поддерживает технологию TrustZone для обеспечения защищенных транзакций, поддержки системы защиты цифрового контента Digital Rights Management (DRM), а также системы энергосбережения IEM.

Cortex-A8 NEON Чип Cortex-A8 представляет собой оптимизированный суперскалярный процессор с возможностью одновременной обработки нескольких инструкций и производительностью уровня 2.0 DMIPS на МГц. Процессор включает в себя 16 Кб или 32 Кб кэша L1, а также, в зависимости от исполнения, различное количество кэша L2 (от 64 Кб до 2 Мб). Среди других архитектурных особенностей чипа Cortex-A8 следует отметить 13 стадий конвейера со значительно улучшенной динамичной технологией предсказания ветвления (10 стадий для NEON).

Финальные варианты Cortex-A8 будут работать на тактовых частотах свыше 600 МГц, при этом, в случае производства с использованием норм 65 нм техпроцесса, энергопотребление ARM Cortex-A8 составит менее 300 мВт, а площадь ядра при этом составит всего 4 мм² (только ядро, без модулей NEON, Trace и кэша L2). Наиболее производительные образцы Cortex-A8 для бытовой техники будут работать на тактовых частотах до 1 ГГц и выпускаться с соблюдением норм 90 нм и 65 нм техпроцессов.

Сравнительная производительность Cortex-A8 В настоящее время ARM уже получила пять лицензионных заявок на Cortex-A8, в числе партнеров - Freescale, Matsushita, Samsung, Texas Instruments. Появление библиотек Advantage-CE под чипы ARM Cortex-A8 на 65 нм техпроцесс ожидается в первом квартале 2006 года.

Процессорные планы ARM В плане охвата рынка многоядерными решениями у ARM также есть свои наработки, например, не представленный на конференции 4-ядерный чип ARM11 - ARM11 MPCore, с производительностью порядка 2640 DMIPS. Архитектура StarCore V5: ждём в новых телефонах MotorolaКалифорнийская компания StarCore LLC, сформированная в июне 2002 года в качестве дочернего совместного предприятия Motorola (ныне Freescale), Agere Systems, Infineon Technologies AG и специализирующаяся на разработке и производстве DSP, представила в рамках Fall Processor Forum 2005 новую архитектуру StarCore V5, нацеленную на применение в новых поколениях беспроводных карманных ПК и мультимедийных устройств. Ключевые плюсы архитектуры StarCore V5, заявленные разработчиками – поддержка 47 новых инструкций, улучшенное предсказание ветвлений и оптимизированная обработка SIMD (single-instruction multiple-data) инструкций. К тому же новая архитектура V5 полностью совместима с прежними разработками StarCore - V2 (SC1200 и SC1400), V3 и V4 (SC2200 и SC2400) на бинарном уровне.  Новая архитектура StarCore V5, представленная в виде первого чипа нового поколения - SC3000, оптимизирована для работы на тактовых частотах до 1 ГГц при изготовлении с соблюдением типичных для нынешней индустрии 90 нм норм техпроцесса. Предполагается, что на базе архитектуры StarCore V5 будут создаваться конечные решения для обработки мощного мультимедийного контента вроде высококачественного декодирования видео в реальном времени.  Ожидается, что первые массовые решения на базе архитектуры StarCore V5 появятся в самом начале 2006 года. По крайней мере, компания Motorola планирует применять этот DSP в своих телефонах поколений 2.5G и 3G, Freescale будет использовать в беспроводных базовых станциях серии Starlite, компании Skyworks, Motorola и Freescale – в сотовых модемах и мультимедийных приложениях, Zultys Technologies и Legerity – в VoIP системах. 104 новых 128-битных SIMD инструкций ARC - всё для мобильного 3D и видеоЕщё один интересный анонс в дни Fall Processor Forum 2005 был представлен компанией ARC International, которая анонсировала набор 104 новых 128-битных SIMD (Single Instruction Multiple Data) инструкций для интенсивной обработки мультимедийных приложений. Набор новых SIMD инструкций ARC полностью совместим с пакетами 16- и 32-битных инструкций ARCompact и будет поддерживаться семейством конфигурируемых процессоров ARC700. С помощью нового набора инструкций чипы класса ARC750D смогут ускорить обработку данных кодеками MPEG 1/2/4, H.264 и VC1 чуть ли не на порядок. Подобные чипы в настоящее время здорово востребованы производителями телефонов, смартфонов, карманных ПК коммуникаторов для интенсивной обработки видео. Похоже, разработку ARC International уже оценили специалисты, поскольку компания успела получить за набор новых SIMD инструкций диплом Product of the Year Award на параллельно проходившей конференции Global Signal Processing Conference (GSPx).  В целом, компании есть чем гордиться, особенно с учетом того, что, например, ее 533 МГц чип ARC750D, который полностью совместим с новыми SIMD инструкциями, обладает площадью всего 9 мм² при изготовлении с соблюдением норм 0,13 мкм техпроцесса. Для сравнения, подобный DSP от близкого конкурента Videantis обладает площадью порядка 42 мм. Особенностью реализации технологии также можно назвать обработку нового набора SIMD инструкций ARC на полной тактовой частоте, в то время как при отсутствии нагрузки чип снижает тактовую частоту и, соответственно, энергопотребление. Вместо "Итого"Не скрою, нравятся мне глобальные события калибра Fall Processor Forum. В течение нескольких дней, собравшись в одном месте, множество представителей известных компаний делятся друг с другом наработками и планами на будущее, своими докладами фактически определяя это будущее на несколько ближайших лет. Увы, за рамками этого рассказа остались многие инновации, представленные на Fall Processor Forum 2005. Не дошли руки до рассказа о представленных компанией Texas Instruments новых 200 - 300 МГц DSP серии TMS320C672x, предназначенных для обработки аудио данных, не вошел рассказ о трех новых 32-битных MCU от Philips Semiconductor на базе ядра ARM7TDMI - LPC2101, LPC2102 и LPC2103, недорогих и весьма эффективных. Не вошел рассказ о новых конфигурируемых процессорах Xtensa 6 от компании Tensilica, не вошли интересные презентации Broadcom, Azul Systems, Innovative Silicon, Green Hills Software и многих других, посвященные аппаратным особенностям реализации современных многоядерных процессорных архитектур и вопросам их программной поддержки. В едином материале просто невозможно отразить всё множество интересных событий, проходящих в столь сжатые сроки, ибо на очереди – новые форумы, новые открытия и анонсы. И ещё немного жаль, что на столь представительном форуме не присутствовали все лидеры индустрии, от этого мероприятия подобного класса только бы выиграли. Впрочем, проблемы в этом нет, ибо всегда можно сравнить результаты разработок, представленные на этой конференции с технологиями, уже анонсированными на других мероприятиях, было бы желание. В заключение отмечу, что на этом события Fall Processor Forum 2005 не заканчиваются, ибо в середине ноября ожидается "вторая серия" - Microprocessor Forum Japan 2005, где среди докладчиков ожидаются представители Toshiba, NEC, Fujitsu, IBM и многих других компаний. До конца года произойдёт ещё очень много интересного…  Автор: Владимир Романченко |

| ||||||||||||||||

| ||||||||||||||||

| Copyright © CompDoc.Ru | ||||||||||||||||

| При цитировании и перепечатке ссылка на www.compdoc.ru обязательна. Карта сайта. |